印刷回路基板(PCB)リバースエンジニアリングの主な目的は、コンポーネントが相互接続されている方法を分析することにより、電子システムまたはサブシステムの機能を決定することです。n

layer間隔は約2milで、総厚さはわずか29.5mil(0.75mm)です。 。---

---figure 5:グラスファイバースクラッチブラシをPCBで使用します(左)。はんだマスクの面積(1.1インチx 0.37インチ)を1分未満(右)で除去しました。

figure 6:TP Tools Skat Blast 1536 Champion Abrasive Blast Cabinet(左)とインテリアビューとターゲットPCBを示すインテリアビューとノズルの理想的な位置決め(右)。

figure 8:ワークスペースのワークスペース化学除去実験。

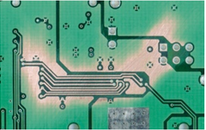

figure 7:研磨爆発後のPCBの上側(左)。 235x倍率(右)は、PCB表面の孔食をより詳細に示しています。

figure 9:30分後(左)、60分(中央)の後のRistoff C8の結果、および90分(右)130°Fに浸る。n

figure 12:レーザーアブレーションを介して除去されたはんだマスクの小さな領域(1.22x 0.12)。-

figure 14:DREMELツールを使用して、基板(左)と結果の内側層(右)を介してレイヤー3を露出します。

figure 15:t

tech QuickCircuit 5000 PCBプロトタイピングシステムとホストラップトップを実行しているラップトップISOPRO 2.7。

""

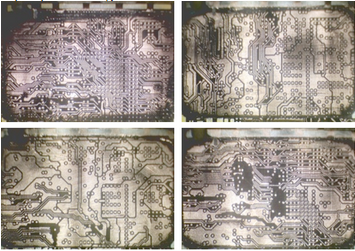

figure 17:CNCミリングで達成されたiPhone 4ロジックボードの一部(左上から始まる時計回り)の内側のレイヤー2〜5。

-

figure 18:blohm refimat cnc cncクリープフィード表面グラインダー。n--

figure 20:dage xd7500vr xrayシステム(左)rayチャンバー(右)。-

figure 21:xlayer pcbの画像、トップダウン(左)および角度のある近接-up(右右) )。-

--figure 22:vgstudio 2.1からのスクリーンショットx、y、zのx交差-セクションビュー。n

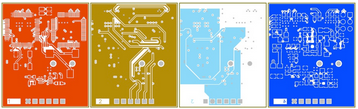

-figure 23:emic 2の画像の画像PCB。フィールドofviewは、ボードの下部センターエリアに限定されていました。 4つのレイヤー(左から右)は、図1の既知のレイアウトに一致するように確認されました。

--

会社の電話番号: +8613923748765

Eメール: お問い合わせ

携帯電話: +86 13923748765

ウェブサイト: pcbfactory.b2bjp.com

住所: Building M, Shajingheyi West Chuangye Industrial Park, Baoan District, Shenzhen City, Guangdong Province